### **Optimization Strategies**

#### - Global Memory Access Pattern and Control Flow

Invent the Future

#### Optimization Strategies

- Global Memory Access Pattern (Coalescing)

- Control Flow (Divergent branch)

## **Global Memory Access**

#### > Highest latency instructions: 200-400 clock cycles

Likely to be performance bottleneck

#### > Optimizations can greatly increase performance

- Best access pattern: Coalescing

- Up to 10x speedup

### **Coalesced Memory Access**

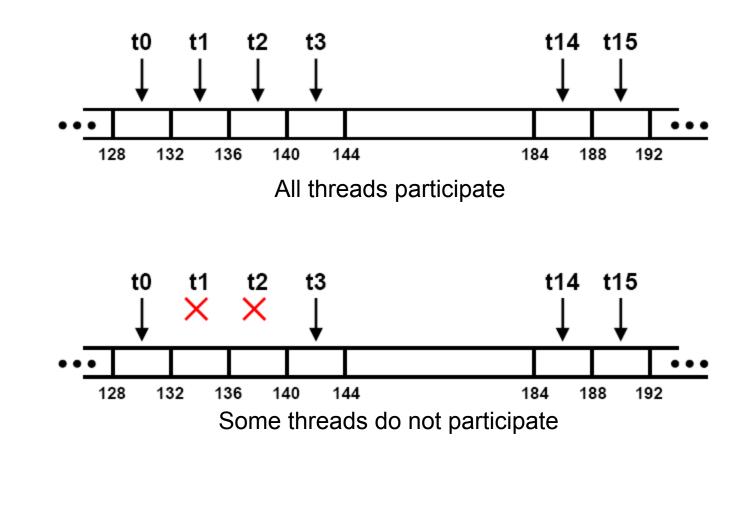

> A coordinated read by a half-warp (16 threads)

#### > A contiguous region of global memory:

- ➢ 64 bytes each thread reads a word: int, float, …

- > 128 bytes each thread reads a double-word: int2, float2, ...

- > 256 bytes each thread reads a quad-word: int4, float4, ...

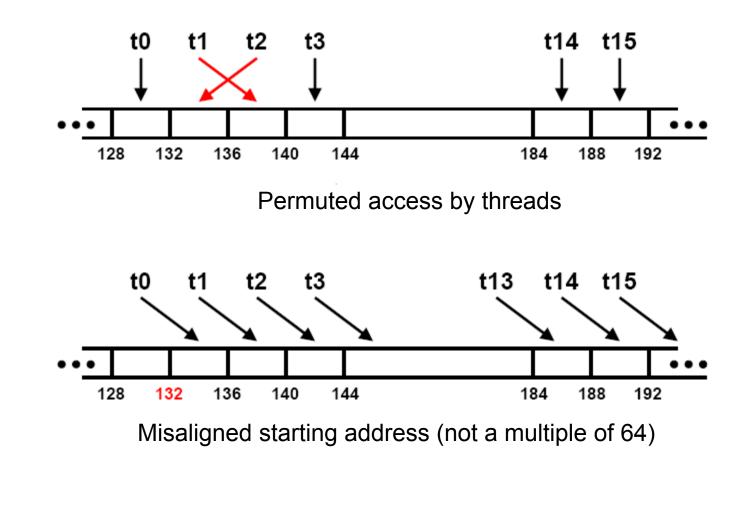

#### > Additional restrictions on G8X architecture:

- Starting address for a region must be a multiple of region size

- The k<sup>th</sup> thread in a half-warp must access the k<sup>th</sup> element in a block being read

#### > Exception: not all threads must be participating

> Predicated access, divergence within a halfwarp

VirginiaTech

Invent the Future

### **Coalesced Access: Reading floats**

irginiaTech

Invent the Future

### **Non-Coalesced Access: Reading floats**

```

rginialech

Optimization Strategies

Invent the Future

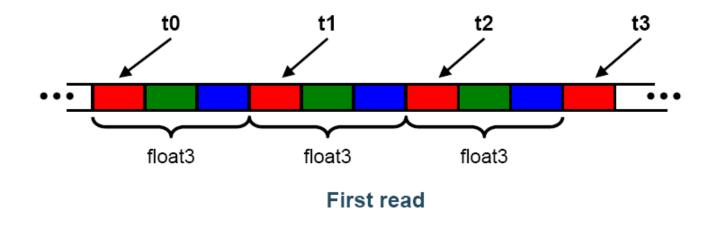

Example: Non-coalesced float3 read

global void accessFloat3(float3 *d in, float3 d out)

int index = blockIdx.x * blockDim.x + threadIdx.x;

float3 a = d in[index];

a.x += 2;

a.y += 2;

a.z += 2;

```

```

d_out[index] = a;

```

### Example: Non-coalesced float3 read (Cont')

#### float3 is 12 bytes

#### Each thread ends up executing 3 reads

- > sizeof(float3)  $\neq$  4, 8, or 12

- Half-warp reads three 64B non-contiguous regions

### Example: Non-coalesced float3 read (2)

Similarly, step 3 start at offset 512

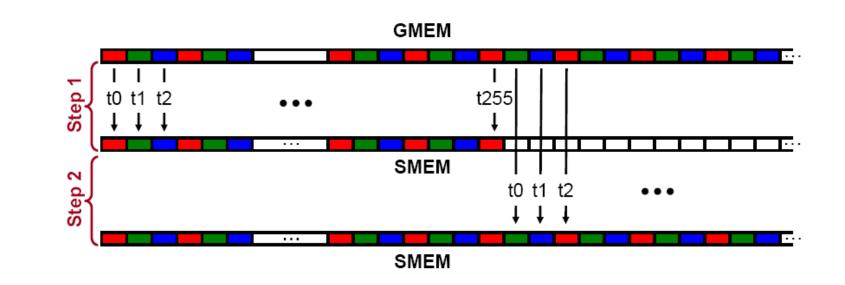

# Example: Non-coalesced float3 read (3)

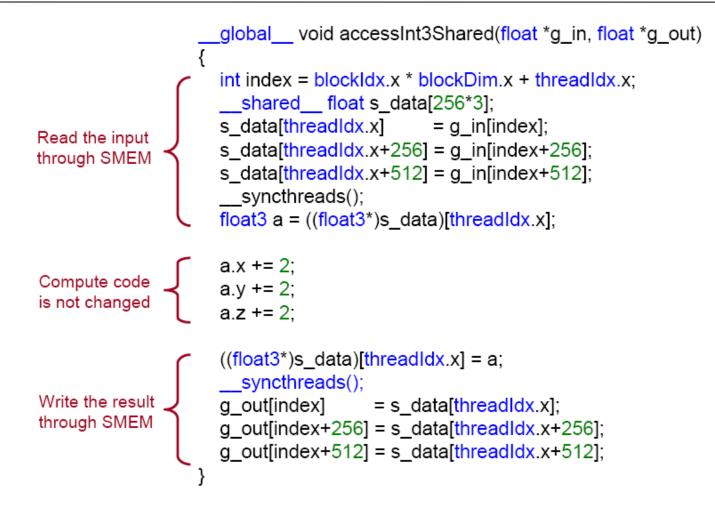

#### Use shared memory to allow coalescing

- Need sizeof(float3)\*(threads/block) bytes of SMEM

- Each thread reads 3 scalar floats:

- Offsets: 0, (threads/block), 2\*(threads/block)

- > These will likely be processed by other threads, so sync

#### Processing

Each thread retrieves its float3 from SMEM array

- Cast the SMEM pointer to (float3\*)

- Use thread ID as index

- Rest of the compute code does not change!

Invent the Future

### Coalescing: Structure of Size ≠ 4, 8, 16 Bytes

- Use a structure of arrays instead of Array of Structure

- > If Array of Structure is not viable:

- > Force structure alignment: <u>align(X)</u>, where X = 4, 8, or 16

- Use SMEM to achieve coalescing

# **Control Flow Instructions in GPUs**

#### Main performance concern with branching is divergence

- > Threads within a single warp take different paths

- Different execution paths are serialized

- The control paths taken by the threads in a warp are traversed one at a time until there is no more.

## **Divergent Branch**

Invent the Future

#### A common case: avoid divergence when branch condition is a function of thread ID

- > Example with divergence:

- > If (threadIdx.x > 2) { }

- > This creates two different control paths for threads in a block

- Branch granularity < warp size; threads 0 and 1 follow different path than the rest of the threads in the first warp</p>

- > Example without divergence:

- > If (threadIdx.x / WARP\_SIZE > 2) { }

- Also creates two different control paths for threads in a block

- Branch granularity is a whole multiple of warp size; all threads in any given warp follow the same path

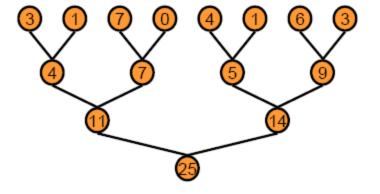

### **Parallel Reduction**

- Given an array of values, "reduce" them to a single value in parallel

- Examples

- sum reduction: sum of all values in the array

- Max reduction: maximum of all values in the array

- Typically parallel implementation:

- Recursively halve # threads, add two values per thread

- Takes log(n) steps for n elements, requires n/2 threads

Copyright © 2013 by Yong Cao, Referencing UIUC ECE498AL Course Notes

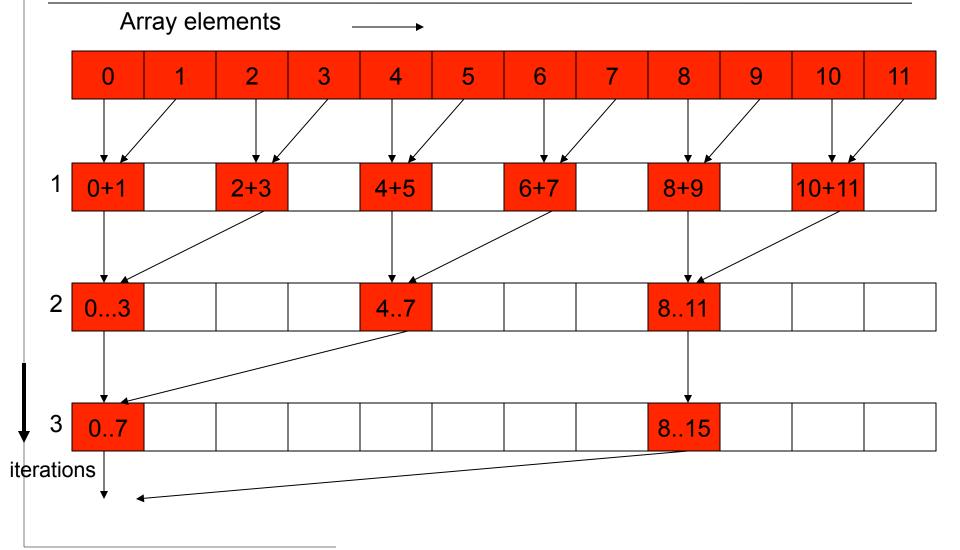

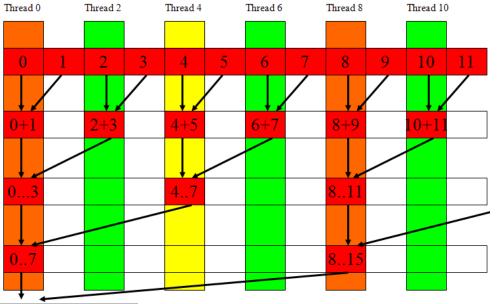

## **A Vector Reduction Example**

nvent the Future

### Assume an in-place reduction using shared memory

- > The original vector is in device global memory

- The shared memory used to hold a partial sum vector

- Each iteration brings the partial sum vector closer to the final sum

- The final solution will be in element 0

### **Vector Reduction**

VirginiaTech

Invent the Future

1872

# A simple implementation

rginia lech

Invent the Future

}

```

__global__ void reduce0(int *g_idata, int *g_odata) {

extern __shared__ int sdata[];

```

// each thread loads one element from global to shared mem unsigned int tid = threadIdx.x; unsigned int i = blockIdx.x\*blockDim.x + threadIdx.x; sdata[tid] = g\_idata[i]; \_\_syncthreads();

```

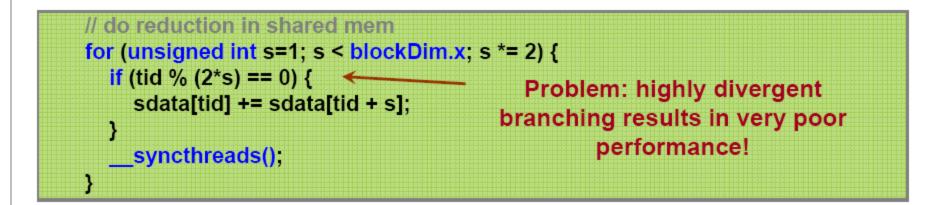

// do reduction in shared mem

for(unsigned int s=1; s < blockDim.x; s *= 2) {

if (tid % (2*s) == 0) {

sdata[tid] += sdata[tid + s];

}

____syncthreads();

}

// write result for this block to global mem

if (tid == 0) g_odata[blockIdx.x] = sdata[0];</pre>

```

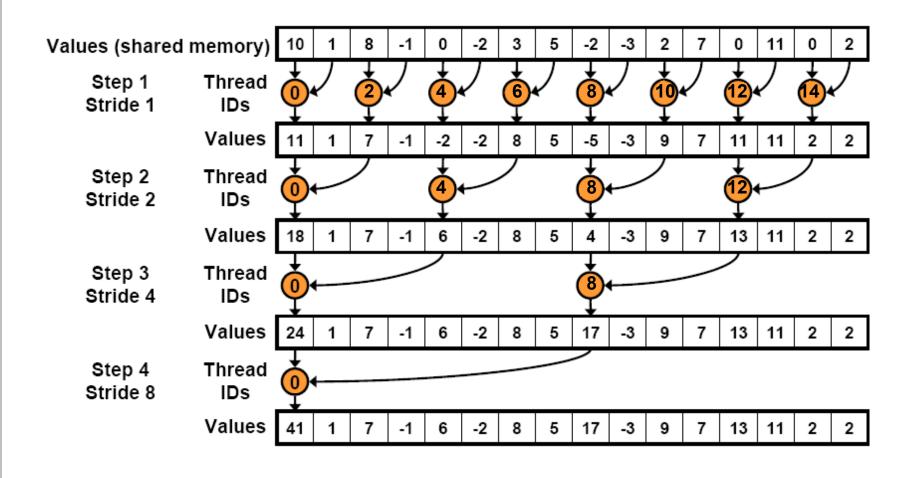

### **Interleaved Reduction**

VirginiaTech

Invent the Future

### **Some Observations**

# In each iterations, two control flow paths will be sequentially traversed for each warp

- > Threads that perform addition and threads that do not

- Threads that do not perform addition may cost extra cycles depending on the implementation of divergence

# Some Observations (Cont')

rginiallech

Invent the Future

- > No more than half of threads will be executing at any time

- > All odd index threads are disabled right from the beginning!

- On average, less than ¼ of the threads will be activated for all warps over time.

- After the 5<sup>th</sup> iteration, entire warps in each block will be disabled, poor resource utilization but no divergence.

- This can go on for a while, up to 4 more iterations (512/32=16= 2<sup>4</sup>), where each iteration only has one thread activated until all warps retire

roinia'lech

Invent the Future

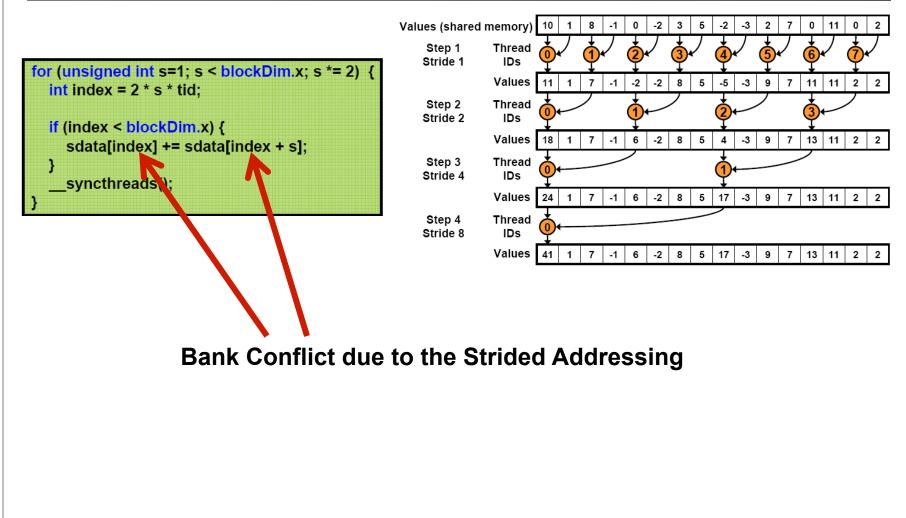

for (unsigned int s=1; s < blockDim.x; s \*= 2) {

if (tid % (2\*s) == 0) {

sdata[tid] += sdata[tid + s];

}

\_\_\_syncthreads();

}</pre>

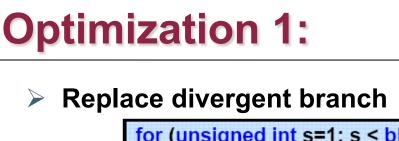

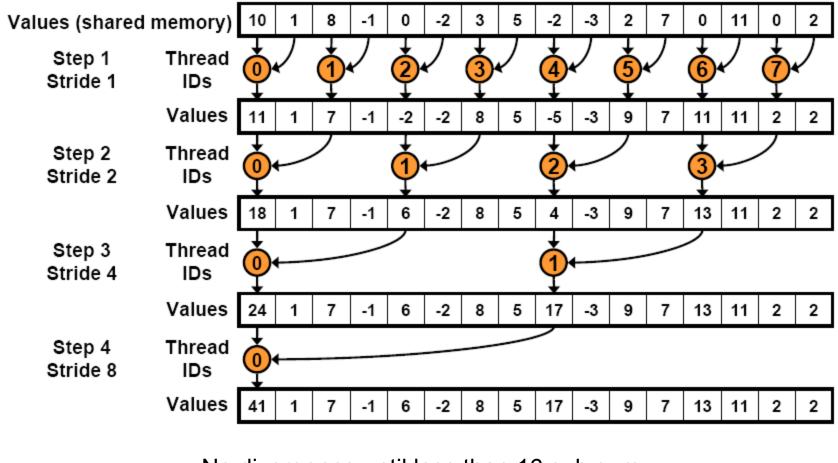

With strided index and non-divergent branch

```

for (unsigned int s=1; s < blockDim.x; s *= 2) {

int index = 2 * s * tid;

if (index < blockDim.x) {

sdata[index] += sdata[index + s];

}

___syncthreads();

}</pre>

```

# **Optimization 1: (Cont')**

VirginiaTech

Invent the Future

No divergence until less than 16 sub sum.

irginiaTech

Invent the Future

# **Optimization 1: Bank Conflict Issue**

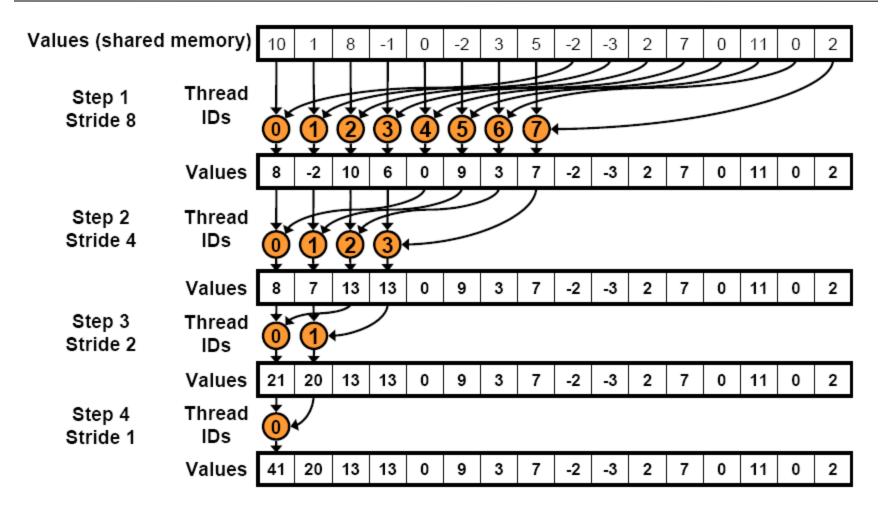

# **Optimization 2: Sequential Addressing**

### **Optimization 2: (Cont')**

#### Replace strided indexing

```

for (unsigned int s=1; s < blockDim.x; s *= 2) {

int index = 2 * s * tid;

if (index < blockDim.x) {

sdata[index] += sdata[index + s];

}

____syncthreads();</pre>

```

With reversed loop and threadID-based indexing

```

for (unsigned int s=blockDim.x/2; s>0; s>>=1) {

if (tid < s) {

sdata[tid] += sdata[tid + s];

}

___syncthreads();

}</pre>

```

#### **Some Observations About the New Implementation**

#### Only the last 5 iterations will have divergence

### Entire warps will be shut down as iterations progress

- For a 512-thread block, 4 iterations to shut down all but one warps in each block

- Better resource utilization, will likely retire warps and thus blocks faster

- Recall, no bank conflicts either